High quality TEM lamella preparation and on-tip analysis using LayerProbe and the OmniProbe 400

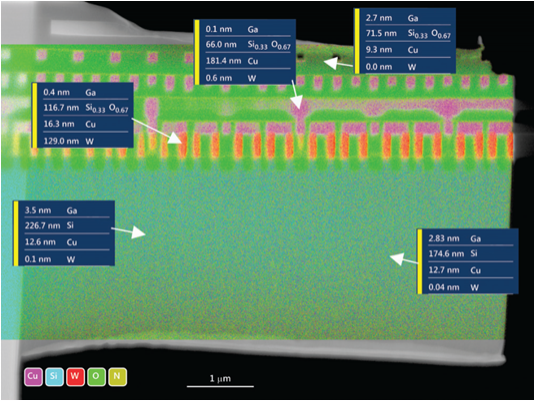

Here we present a new technique that enables measurement of the local thickness and composition of TEM lamellae and discuss its application to the failure analysis of semiconductor devices.